삼성전자(005930), TSMC, 인텔 등 세계적인 회사들이 ‘1나노’ 반도체 공정 개발에 나섰다. 인공지능(AI) 시대 개막 및 IT 고도화에 대응하기 위한 초미세 회로 공정으로, 향후 수년 내 각 회사의 반도체 경쟁력을 판단할 수 있는 핵심 기술이 될 것으로 예상된다.

세계 파운드리 업계 1위인 TSMC는 23일(현지시간) 미국 캘리포니아 실리콘밸리에서 열린 ‘2025 TSMC 북미 테크 심포지움’ 행사 1.4나노(㎚·10억분의 1m) 기술을 적용한 반도체 칩을 2028년부터 생산할 계획이라고 밝혔다.

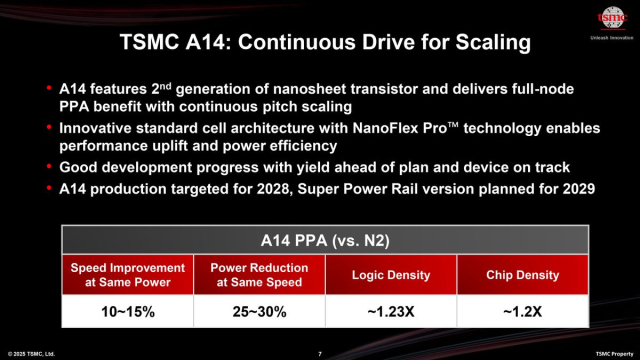

케빈 장 TSMC 수석부사장은 "A14(1.4나노)는 완전한 노드 전환 기반의 차세대 첨단 실리콘 기술"이라며 "N2(2나노 공정) 대비 속도는 최대 15% 빠르고, 전력 소비는 30% 줄어들며 트랜지스터 집적도는 1.23배 향상됐다"고 말했다.

1.4나노 공정은 현재의 3나노 공정과 TSMC가 올해 말 생산에 들어가는 2나노 공정을 넘어서는 최첨단 기술이다. TSMC는 내년 말에는 중간 단계로 1.6나노 공정 기술도 도입할 예정이라고 지난해 밝힌 바 있다.

TSMC는 이 최첨단 공정에 트랜지스터의 성능과 전력 효율을 획기적으로 높인 게이트올어라운드(GAA) 2세대를 기반으로 한다.

파운드리 업계 2위인 삼성전자 파운드리 사업부 역시 1나노 반도체를 개발하고 있다. 삼성 파운드리는 올해 시설 투자 규모를 지난해 대비 절반 수준으로 줄인 상황에서도, 평택 사업장에 1.4나노 시험라인 구축을 계획하는 등 이 공정에 관심이 많다. 삼성전자는 1.4나노 공정을 TSMC보다 1년 빠른 2027년에 양산하는 것을 목표로 하고 있다.

또한 삼성전자 반도체연구소는 최근 2나노 등 최선단 공정 개발에 참여해 온 연구원들 일부를 차출해 1나노 공정 프로젝트팀을 구성했다.

인텔은 1.8나노급인 18A 공정을 올 하반기부터 양산하면서 삼성전자, TSMC보다 먼저 1나노대 공정에 진입하기 위해 적극적으로 투자하고 있다. 인텔은 최근 공개된 VLSI 2025 심포지엄의 논문 초록을 통해 18A 공정이 '인텔 3' 공정 대비 밀도와 성능, 전력 소모 등에서 상당히 개선됐다고 밝혔다.

< 저작권자 ⓒ 서울경제, 무단 전재 및 재배포 금지 >